# **Structure of the SemiConductor Tracker Detector Control System**

| Prepared by :   |                                       | Checked by: |  | Approved by:            |                 |  |                                |

|-----------------|---------------------------------------|-------------|--|-------------------------|-----------------|--|--------------------------------|

| Richard BRENNER |                                       |             |  |                         |                 |  |                                |

|                 |                                       |             |  |                         |                 |  |                                |

|                 | for information,<br>you can contact : | R. Brenner  |  | Tel.<br>+46–18–471 7616 | Fax<br>+46-18-4 |  | E-Mail<br>brenner@mail.cern.ch |

| Structure of the SemiControl | Page 2 of 15        |                      |                    |

|------------------------------|---------------------|----------------------|--------------------|

| ATL-IS-ES-0011               | Created: 8–Feb–2001 | Modified: 8–Feb–2001 | Rev. No.: <b>0</b> |

# Distribution:

| Issue Revision                | Date                             | Sheet | Description of Change                                                                                                                | Release |

|-------------------------------|----------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------|---------|

| Draft 1<br>Draft 2<br>Draft 3 | 99–11–17<br>01–04–08<br>01–10–04 |       | This is the first draft version of this document Improved version of the document Improvements to cooling and interlock descriptions |         |

|                               |                                  |       |                                                                                                                                      |         |

|                               |                                  |       |                                                                                                                                      |         |

|                               |                                  |       |                                                                                                                                      |         |

|                               |                                  |       |                                                                                                                                      |         |

This document will describe of the structure of the Detector Control System (DCS) for the SemiConductor Tracker (SCT) which should meet the requirements written in the The SemiConductor Tracker Detector Control System Requirements Document [1]. The detailed architecture of the DCS strongly depends on the structure of the general DCS system of the ATLAS experiment and on electrical architecture of the SCT and mechanical issues on routing services and mounting sensors onto mechanical structures. The intention for the SCT DCS is to follow the general ATLAS DCS system architecture as much as possible unless there are special reasons where the SCT needs tailored solutions. By conforming to the general DCS structure the system of the SCT will be easy to maintain in the future by any DCS expert.

Monitoring of dose rates and total dose is not included in this document. The monitoring of radiation inside the ATLAS Inner Detector may be important for all subdetectors and should have a common solution.

# 2. Main components in the SCT DCS

The main components in the DCS of SCT are:

- High Voltage power supply (HV)

- Low Voltage power supply (LV)

- Environment monitoring of temperature, humidity, barometric pressure

- Alignment system

- · Cooling system

- · Interlock system

- Local Control Station (LCS)

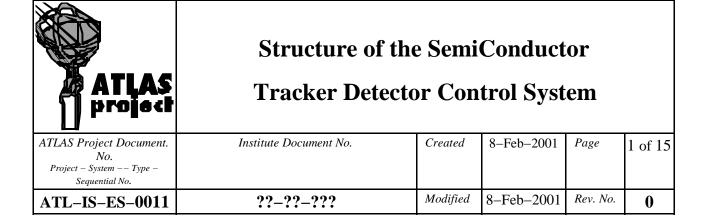

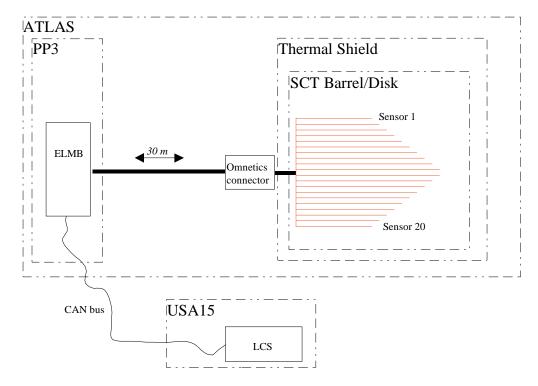

The three first listed components are directly linked to silicon detector modules. The alignment system and cooling system are autonomous systems with no direct electrical contact to the detector modules. The interlock system will mainly link the cooling system directly to the power supplies but there will also be interlock between the optical readout, a part of the Data Acquisition System, and the power supplies. The LCS, which is the interface between the general DCS for ATLAS and the sub detector DCS, is hierarchically higher than the rest of the listed components. The LCS can be run stand alone without the main ATLAS DCS. The LCS connects to other components of DCS via numerous interface cards. The DCS system will support several protocols driving fieldbus nodes such as CAN—bus (Controller Area Network), Local Area Network (LAN) etc.. Figure 1 shows the partitions in the SCT sub detector branch of the ATLAS DCS.

| Structure of the SemiC | Page 4 of 15        |                      |                    |

|------------------------|---------------------|----------------------|--------------------|

| ATL-IS-ES-0011         | Created: 8–Feb–2001 | Modified: 8–Feb–2001 | Rev. No.: <b>0</b> |

Figure 1. A shematic drawing of the DCS partitions.

### 3. Architecture of the DCS

The host of DCS subsystem, the LCS, can be be operated in stand alone mode which is important during the commissioning phase. The LCS is the interface module between the general DCS running Supervisory Control and Data Acquisition (SCADA) software and Programmable Logic Controller (PLC) based input—output modules.

The DCS for SCT can be split on several LCS if this improves flexibility in the commissioning phase. Two different scenarios of splitting the DCS on LCS is considered:

- 1. One LCS for combined HV, LV and environment monitoring, separate LCS for cooling plant and alignment system.

- 2. Barrel and endcap structures on separate LCS.

The assembly procedure may benefit from option 2 which would give a fully functional mini DCS during testing. A feature of modern control systems is to have the electronics components distributed in the experiment which will

driving a CAN-bus is called node and an electronics component attached to the CAN-bus is called unit which can be a Local Monitoring Box for environment monitoring or a power supply crate controller.

The number of units connected to one node will mainly depend on the maximum data load expected from the units. The length of the CAN bus will determine the maximum recommended transfer rate on the bus. The recommended bitrata are listed in table 1.

| Bitrate [kbits/s] | Cable length [m] |

|-------------------|------------------|

| 10                | 6700             |

| 20                | 3300             |

| 50                | 1300             |

| 125               | 530              |

| 250               | 270              |

| 500               | 130              |

| 1000              | 40               |

Table 1.Recommended bitratas vs. cable length.

Expected cable lengths in the final experiment will be around 100–200 m giving a conservative transfer rate of 250 kbits/s. Data from a single monitoring value will be transferred in 1/500 second – 1/200 second depending on which transfer protocol will be used and maximum occupancy allowed on the CAN–bus. Assuming a full set of data has to be transferred in 15 seconds the maximum number of monitoring values per CAN–node is between 3000 and 7500. In steady state operation of the DCS system the transfer rates will very low since only data outside pre set limits will be transferred unless full set of data is requested for database updates.

## 4. Number of channels in DCS

The number of values to be monitored and controlled in SCT are listen in tables 2 to 6.

| Description                            | Sensors | Wires           | Conductor     |

|----------------------------------------|---------|-----------------|---------------|

| Module temperature                     | 4224    | 3 per 2 sensors | Low Mass Tape |

| Temperature of cooling pipe            | 264     | 4 per sensor    | Twisted Pair  |

| Air temperature                        | 160     | 2 per sensor    | Twisted Pair  |

| Thermal shield                         | 60      | 2 per sensor    | Twisted Pair  |

| Mechanical structures                  | 48      | 2 per sensor    | Twisted Pair  |

| Temperature along cable routing        | 380     | 2 per sensor    | Twisted Pair  |

| Humidity                               | 16      | 6 per sensor    | Twisted Pair  |

| Barometric pressure                    | 2       | 6 per sensor    | Twisted Pair  |

| Regulation of cooling system           | 88      | 2 per sensor    | Twisted Pair  |

| Interlock sensors (shared with cooling | g pipe) |                 |               |

Table 2. Channels to be monitored inside barrel SCT.

| Description                            | Sensors | Wires           | Conductors    |

|----------------------------------------|---------|-----------------|---------------|

| Module temperature                     | 1976    | 3 per 2 sensors | Low Mass Tape |

| Temperature of cooling pipe            | 320     | 4 per sensor    | Twisted Pair  |

| Air temperature                        | 160     | 2 per sensor    | Twisted Pair  |

| Thermal shield                         | 120     | 2 per sensor    | Twisted Pair  |

| Mechanical structures                  | 72      | 2 per sensor    | Twisted Pair  |

| Temperature along cable routing        | 360     | 2 per sensor    | Twisted Pair  |

| Humidity                               | 16      | 6 per sensor    | Twisted Pair  |

| Barometric pressure                    | 4       | 6 per sensor    | Twisted Pair  |

| Regulation of cooling system           | 80      | 2 per sensor    | Twisted Pair  |

| Interlock sensors (shared with cooling | g pipe) |                 |               |

Table 3. Channels to be monitored inside forward SCT.

| Structure of the SemiControl | Page 6 of 15        |                      |                    |

|------------------------------|---------------------|----------------------|--------------------|

| ATL-IS-ES-0011               | Created: 8–Feb–2001 | Modified: 8–Feb–2001 | Rev. No.: <b>0</b> |

| Description    | Values |

|----------------|--------|

| LV voltage     | 10560  |

| LV current     | 10560  |

| LV temperature | 528    |

| HV voltage     | 2112   |

| HV current     | 2112   |

| HV temperature | 264    |

Table 4. Monitoring channels for barrel power supplies.

| Description    | Values |

|----------------|--------|

| LV voltage     | 9880   |

| LV current     | 9880   |

| LV temperature | 2470   |

| HV voltage     | 1976   |

| HV current     | 1976   |

| HV temperature | 1235   |

Table 5.. Monitoring channels for forward power supplies.

| Description               | Values |

|---------------------------|--------|

| LV overcurrent trip level | 20440  |

| LV voltage                | 20440  |

| HV overcurrent trip level | 4088   |

| HV voltage                | 4088   |

| Cooling system            |        |

Table 6. Controlled values in SCT.

# 5. Implementation and grouping of DCS components

#### 5.1 Monitoring inside SCT volume

The environment inside the SCT will be monitored for temperature, barometric pressure and humidity. All sensors, services and cables have to be radiation hard up to  $2 \cdot 10^{14}$  n/cm2 (1 MeV neutron equivalent) an 10 Mrad ionising dose. Temperature except the module temperature will be monitored by platinum pt1000 sensors using two wire readout. Sensors included in the hard—wire interlock will be read out by four wires. The humidity will be sensed with a compact strain gauge senor which measures the relative humidity. The humidity is ratio of two measured resistance of typically a few hundred Ohms hence the wires have to be doubled to correct for the resistance in the cable. The sensor for barometric pressure is still under investigation. All the environmental parameters expect for module temperatures will be read out by LMBs which are placed in low radiation environment at the third patch panel, PP3.

#### Module temperature

For silicon microstrip detector modules temperature will be monitored on the electronics hybrids. The barrel has two sensors, one for each hybrid bridge, and the forward modules have one, because of the end-tap design. The measured temperature will give an indication off the thermal resistance between the detector module and the cooling pipe. If the contact to the cooling pipe is very bad the module can be switched off avoiding thermal damage to the detector module. The temperature readout will be done by the power supply unit which also separately biases every temperature sensor. The wiring of the sensors are integrated with the power cables to the detector module. Two lines in the low mass tapes are reserved for temperature readout, the return line for the digital ground will be shared for temperature monitoring. The low mass tapes will bring the signals to patch panels PPB2/PPF2 on the cryostat wall of the Liquid Argon calorimeter. From PPB2/PPF2 to the SCT electronics crates the routing will be done by custom

copper cables which can more easily pass through the narrow gaps of the cryostat end plate to thick cables routing services to the power supply crates. The monitoring precision for the temperature sensors is specified in SCT–TMP5 and SCT–TMP6 [1] requiring a relative precision better than 0.3 °C and a absolute precision better than 1 °C. The temperature on the module will be sensed with 10 k $\Omega$  NTC thermistors . The thermistors are preferred because of the small package size SMD 0603 (LxWxT= 1.6x0.8x0.5 mm³) while the smallest pt1000 SMD size is 1206 (LxWxT= 3.1x1.56x0.6 mm³). To achieve a relative precision better than 0.3 °C and absolute precision better than 1 °C in the region –20 °C to +50 °C constant voltage or power operation mode is recommended to be implemented in the power supplies. The NTC thermistors have been proven to be radiation hard devices. Two SMD 0603 size NTC thermistors (Taiyo Yuden, Japan: TBPS1S103F345F5Q and Ishizuka, Japan: Semitec 103KT1608–1P) have been irradiated by the pixel community [8] with good results.

#### Temperature of cooling pipes

The cooling system will monitor the temperature minimum for the inlet and the outlet of the cooling pipes and on the vapour return pipe. The temperatures measured on the cooling pipes will be used in the hardwired interlock system and are therefore accounted separately from other items needed for controlling the cooling system. Four wires twisted in pairs will be used for read out of pt1000 sensors or alternatively NTC thermistors in order to achieve maximum stability and accuracy. The routing of the wires have to be well protected for mechanical damage and a natural way is to rout the cooling pipes and the wires together up to the cooling patch panels at PPB1/PPB2/PPF2. Keeping the wires and pipes together will make the installation work easier.

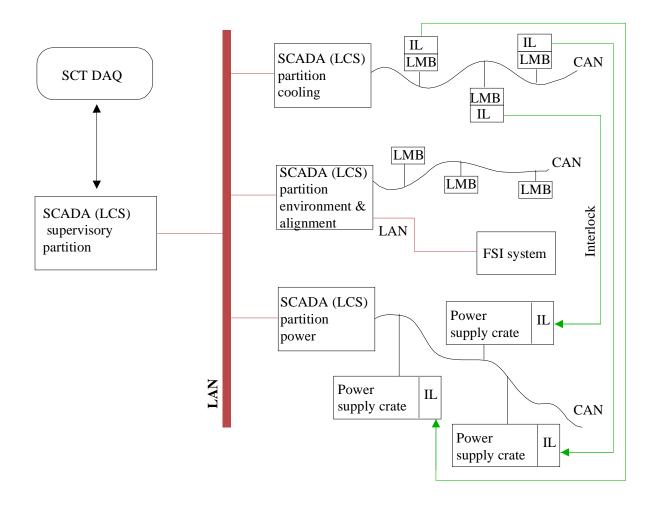

The layout of the cooling are different in the barrel and in on the forward disks. All the barrel cylinders use the same basic cooling circuit shown in figure 2. In the figure the sensors are labelled S1 to S6 and a block of four barrel modules supplied by one LV power supply card are drawn as rectangles on the cooling pipes.

Figure 2. Schematic layout of a barrel cooling unit.

The number of cooling units in the barrel is shown in table 7.

|          | <b>Cooling Units</b> | NTC Sensors | Sensors in interlock | <b>Detector Modules</b> |

|----------|----------------------|-------------|----------------------|-------------------------|

| Barrel 1 | 8                    | 48          | 40                   | 384                     |

| Barrel 2 | 10                   | 60          | 50                   | 480                     |

| Barrel 3 | 12                   | 72          | 60                   | 576                     |

| Barrel 4 | 14                   | 84          | 70                   | 672                     |

| Total    | 44                   | 264         | 220                  | 2112                    |

Table 7. Number of sensors on cooling pipes in the barrel SCT.

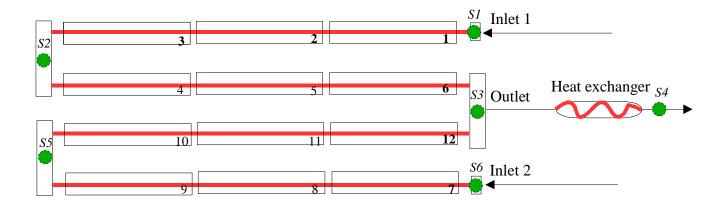

On the wheels every quadrant has an output while the number of inputs depend on the numbers of rings with detector modules on wheels. Figure 3 shows all three cooling circuit layouts for the wheels. Table 8 shows the number of DCS sensors in the forward SCT. Note that the number need to be multiplied by 2 to account for both +Z and -Z part of the forward SCT.

| Structure of the SemiConductor Tracker Detector Control System |                     |                      | Page 8 of 15       |

|----------------------------------------------------------------|---------------------|----------------------|--------------------|

| ATL-IS-ES-0011                                                 | Created: 8–Feb–2001 | Modified: 8–Feb–2001 | Rev. No.: <b>0</b> |

Figure 3. Schematic layout of cooling quadrants on forward wheels.

|         | Inlets | NTC Sensors | Sensors in interlock | <b>Detector Modules</b> |

|---------|--------|-------------|----------------------|-------------------------|

| Wheel 1 | 8      | 16          | 12                   | 92                      |

| Wheel 2 | 12     | 20          | 16                   | 132                     |

| Wheel 3 | 12     | 20          | 16                   | 132                     |

| Wheel 4 | 12     | 20          | 16                   | 132                     |

| Wheel 5 | 12     | 20          | 16                   | 132                     |

| Wheel 6 | 12     | 20          | 16                   | 132                     |

| Wheel 7 | 8      | 16          | 12                   | 92                      |

| Wheel 8 | 8      | 16          | 12                   | 92                      |

| Wheel 9 | 4      | 12          | 8                    | 52                      |

| Total   | 88     | 160         | 124                  | 988                     |

Table 8. Number of sensors on cooling pipes in forward SCT.

#### Air temperature

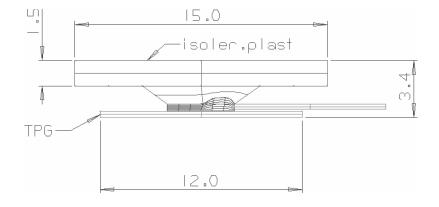

The air temperature inside the SCT will vary with a main temperature gradient expected between top and bottom of the SCT. Knowledge of the air temperature is needed by the FSI alignment system. The temperature of the air inside SCT will be monitored SCT barrel end–flanges and inside the barrel cylinder and on the forward–disks. The engineers will propose locations available for the temperature sensors. The pt1000 sensors will be mounted on pedestals not to have thermal contact with the barrel mechanics and with a plate reducing the risk for self heating making the response time of the sensor slower, figure 4. The pedestal will be mounted on the inner surface of the barrel.

Figure 4. Air temperature sensor for SCT

#### Mechanical structure

The temperature of the mechanical structure will be monitored in points requested by the engineers. The pt1000 sensors will be glued to the surface of the mechanical structure. The size of the sensor is 4 mm x 2.2 mm x 1 mm.

#### Thermal enclosure

Both the forward and barrel SCT will have a thermal enclosure for operation between -10 and -20 degC. The thermal enclosure will have sensors distributed with twice the granularity of the controls for the thermal shield. The pt1000 sensors will be glued to both in– and outsides of the thermal enclosure and read out by twisted pair wires.

#### Temperature along the services

The temperature of the services to SCT will be monitored on average every meter by pt1000 sensors place inside and outside bundles of electrical cables and cooling tubes. The density of sensors will be higher in critical places where the packing factor is high and at patch panels. Inside the Transition Radiation Tracker (TRT) the monitoring will done every 30 cm. The monitoring will be done with a two wire readout connected to ELMBs situated at PP3 or further out in the ATLAS cavern.

#### Humidity

Four humidity sensors will be placed in the barrel region and forward regions respectively. In the barrel region the humidity sensor will be placed close to the air temperature sensor on the innermost and the outermost barrel. In the forward regions the sensors will be but close to the air temperature sensor on the first and the last disks. The monitoring precision for the humidity sensor is specified in SCT-HUM2 [1] requiring a precision better than 1% RH. The only humidity sensor guaranteed for the radiation level inside SCT is the Xeritron<sup>1</sup> sensor. The performance of the Xeritron humidity sensor before and after irradiation, at several relative humidity levels and at various temperatures has been studied [9]. The Xeritron sensor show to be robust to temperature variations and operational after irradiation and at sub zero temperatures. The sensor is has a repeatability of  $\pm 1\%$ , linearity of  $\pm 2\%$  and hysteresis of  $\pm 2\%$  over the range 0–100% RH thus the precision specification cannot be met. The expected performance is between 3–5% over 0–100% RH. The Xeritron sensors are typically delivered encapsulated in tubes with 5.5 mm diameter, 25 mm long. The sensors can be produced for use in SCT without encapsulation, figure 4, with the reduces the size to 20 mm x 4 mm x 1 mm.

<sup>1</sup>Hygrometrix, Inc, PO BOX 2064, ALPINE CA 91903, US

| Structure of the SemiConductor Tracker Detector Control System |                     |                      | Page 10 of 15      |

|----------------------------------------------------------------|---------------------|----------------------|--------------------|

| ATL-IS-ES-0011                                                 | Created: 8–Feb–2001 | Modified: 8–Feb–2001 | Rev. No.: <b>0</b> |

Figure 5. A humidity sensor on the bottom and a pt100 sensor on the top.

#### Barometric pressure

Knowledge of the barometric pressure has been requested by the alignment system. The monitoring precision for the barometric pressure sensor is specified in SCT-PRE2 [1] requiring a precision better than 1 mbar. The barometric pressure will be measure with two sensors inside each thermal enclosure. Since the gas flow will be low the positioning of the sensor is not critical. One candidate sensor<sup>2</sup> has been irradiated and the post-irradiation performance is presently studied. The sensor candidate fits into a 15x10x4 mm<sup>3</sup> volume.

#### Geodetic data

The alignment system is an autonomous system under the ATLAS Detector Control System. The alignment system measures by using Frequency Scanning Interferometry (FSI) distances between different points inside SCT set up in geodetic measurement networks. The data from the measurements will be processed by two workstations connected to the SCT DCS via a Local Area Network (LAN). The drivers and receivers of the FSI system will be hosted in several VME crates in the ATLAS equipment cavern USA–15. For the calculations of geodetic networks the alignment system will need temperature, humidity and barometric pressure data from the DCS. The FSI system will be described in a separate document.

#### **5.2 Monitoring outside SCT volume**

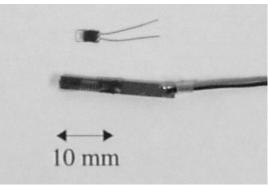

The power supplies are located in an area which can be accessed in contrary to the ATLAS cavern be accessed when LHC is running. Long cables have to be used to bring the services to the SCT. The cables will be routed through several patch panels where the cable type or size will be changed. The power supplies will reside in crates with one crate controller and 12 LV bias cards mixed with 6 HV bias cards. The total number of monitoring points per HV/LV crate is around 580 . A LV bias card hosts 4 LV channels with 4 voltage/current lines each supplying independently 4 modules. The HV bias card hosts 8 channels for 8 modules. All monitoring is done locally in crates. Detailed technical description on the power supplies can be found in [2],[3].

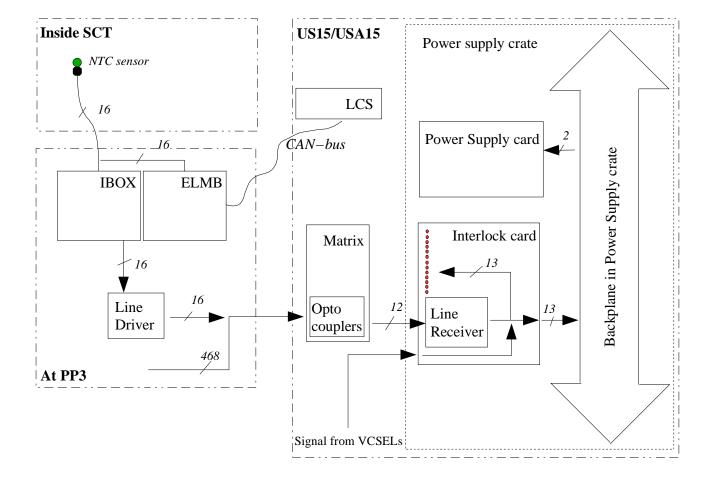

The crate controller of the power supplies will connect to the LCS over the CAN filedbus. In total 76 power supplies crates will be grouped on 8 to 15 CAN fieldbuses. A schematic figure on the configuration of power supplies is shown in figure 6. The power supplies will be connected to the hard—wired interlock system through a separate card. The interlock card will transform the signals from the interlock system to high/low states in the parallel inter crate interlock bus. The interlock system will be described below.

Figure 6 A schematic figure of the power supply configuration.

# 6. Cable routing

The DCS wires except the wires for temperature sensors sensing the cooling pipes will be routed along the same path as the low mass tapes of the silicon detector modules. The wires for the cooling sensors will be routed along the cooling pipes which is a natural routing when the sensors are pre–assembled to the cooling pipes.

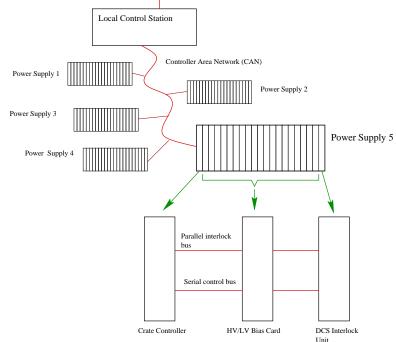

The wires from DCS sensors from each barrel and wheel are routed to 30 or 40 pin connectors by 200 um thick twisted pair copper wires (AWG 32). The size of a robust 40 pin microminiature dual row connector produced by Omnetics<sup>3</sup> is 33 mm x 12 mm x 5 mm. The multipin connector have a pig-tail to the sensors which allows connections outside the SCT thermal shield. A multiconductor cable will bring the signals from the connector at the thermal shield directly to PP3 30 m away from the SCT where the CAN-bus based ELMB boards are mounted. A drawing of a ELMB board is shown in [6]. There will be different number of connectors per barrel and wheel depending on the number of DCS sensors mounted on the structure. A table showing the number of sensors, wires and connectors per barrel and wheel can be found in appendix A.

The DCS sensors on the barrel structure need 16 cables and on the forward wheels 18 cables. The sensors on the thermal shield need 6 cables. In total 40 cables with a diameter 3.2 mm need to be routed from the SCT to PP3. Drawings on the cable dimensions and cross section are show in Appendix 2.

| Structure of the SemiConductor Tracker Detector Control System |                     |                      | Page 12 of 15      |

|----------------------------------------------------------------|---------------------|----------------------|--------------------|

| ATL-IS-ES-0011                                                 | Created: 8–Feb–2001 | Modified: 8–Feb–2001 | Rev. No.: <b>0</b> |

Figure 7. A shematic drawing of the routing of DCS wires.

#### **Grounding of DCS**

The grounding of the SCT is described in "ATLAS SCT/pixel Grounding and Shielding" note by Ned Spencer [4]]. The DCS sensors close to the sensitive front—end electronics, ie sensors for detector module temperature, are handled with special concern. Sensors far away from front—end electronics follow the common ATLAS DCS architecture with a LMB unit biasing the sensors. The LMB unit has external power supplies which are grounded to the SCT shield. The long DCS cables outside the SCT thermal shield have a single shield around the twisted pair wires. The shield of the cable is grounded in the SCT shield.

# 7. Interlock system

The hardwired interlock system is the most important part in the safety thinking of the SCT. The interlock system will act if the actions taken by the software driven SCADA software fails. The interlock system will also prevent the LV power supplies to be switched—on unless the cooling system is working properly. The hardwired interlock system creates a fast hardwired path between cooling system and LV power supplies. The interlock system senses the temperature on the cooling pipes and when the temperature is above an alarm threshold generates an interlock logical signal. The levels of the interlock signal is specified in SCT-ILK10 in reference [1]. The interlock signal is routed from the interlock channel to all the LV bias cards supplying power to modules on the cooling circuit of the interlock channel. The basic unit of the interlock system is the interlock box [5] which shares signals from temperature sensors with the LMB units allowing the temperature values to be used by both the cooling system and the environment monitoring system. The sensors are read out by four wires for maximum stability of the values and routed to the interlock units positioned at PP3. The number of temperature sensors in the interlock system is fewer than the number of silicon detector modules as well as the number of power supply units in SCT. Therefore the interlock logical status has to be re-routed to the correct LV power supply units in a patch panel located in US15/USA15.. In the barrel SCT the power to a stave, with 12 modules, is interlocked if one or both of the temperature sensors positioned in the start or the end of the stave are above threshold, see figure 2. In the forward SCT the same action is taken for modules on a cooling circuit if one or both of the temperature sensors positioned at the inlet and outlet are above threshold., see figure 3. The total number of sensors used by the interlock system is 468. The optical readout system has an interlock acting as well on the power supplies. The granularity of the interlock will depend on the architecture of the off-detector electronics boards for the DAQ system. The structure of the interlock system is shown in figure 8.

Figure 8. A schematic drawing of the interlock system.

In barrel SCT the layout matches perfectly the power supply architecture with one power supply crate powering one cooling unit, see figure 2. One interlock scheme for barrel SCT is shown in table 9, where the positions of modules can be found in figure 2.

| <b>High Temperature</b> | Power supply cards interlocked | <b>Cooling Circuit</b> |

|-------------------------|--------------------------------|------------------------|

| S1                      | 1,2,3                          | Stave 1                |

| S2                      | 1,2,3,4,5,6                    | Stave 1,2              |

| S3                      | 4,5,6,10,11,12                 | Stave 2,4              |

| S5                      | 7,8,9,10,11,12                 | Stave 3,4              |

| S6                      | 7,8,9                          | Stave 3                |

Table 9. Interlock scheme for barrel SCT.

The geometry In forward SCT is more complex than in the barrel and therefore the layout cannot be matched with neither power supply crates nor power supply cards. A interlock scheme for Wheels 2,3,4,5,6 is shown in table 10, for Wheels 1,7,8 is shown in table 11 and for Wheel 9 in table 12. The explanation for S1 to S4 can be found in figure 3.

| <b>High Temperature</b> | # Power supply cards interlocked | <b>Cooling Circuit</b> |

|-------------------------|----------------------------------|------------------------|

| S1                      | 13                               | Outer Ring             |

| S2                      | 10                               | Middle ring            |

| S3                      | 10                               | Inner Ring             |

| S4                      | 33                               | All rings              |

*Table 10. Interlock scheme for Wheels 2,3,4,5,6.*

| Structure of the SemiConductor Tracker Detector Control System |                     |                      | Page 14 of 15      |

|----------------------------------------------------------------|---------------------|----------------------|--------------------|

| ATL-IS-ES-0011                                                 | Created: 8–Feb–2001 | Modified: 8–Feb–2001 | Rev. No.: <b>0</b> |

| <b>High Temperature</b> | # Power supply cards interlocked | Cooling Circuit |

|-------------------------|----------------------------------|-----------------|

| S1                      | 13                               | Outer Ring      |

| S2                      | 10                               | Inner Ring      |

| S3                      | 23                               | All rings       |

Table 11. Interlock scheme for Wheels 1,7,8.

| <b>High Temperature</b> | # Power supply cards interlocked | Cooling Circuit |

|-------------------------|----------------------------------|-----------------|

| S1                      | 13                               | Outer Ring      |

| S2                      | 13                               | Outer Ring      |

Table 12. Interlock scheme for Wheel 9.

## 8. Data flow in the DCS

#### DCS and database

The SCT DCS will be handled according to general ATLAS DCS policy.

### Power supplies and cooling

The cooling system need continuous information about the power load in the SCT in order to set correct flow of coolant in the detector. The information of power load will be transferred from the power supplies via the LCS to the cooling system. A change in the power consumption of the SCT should be known by the cooling system within 3 seconds. If the SCADA system cannot guarantee the needed reasons time the design of the power supplies may need a minor change allowing a status bit be sent by a hard wired bus to the cooling system.

#### DCS and DAQ

Communication between the DCS and Data Acquisition System (DAQ) is described in [7]. The communication will be handled mainly on two levels.

- The DCS database is shared by DAQ. The data is synchronised by time stamp. The real–time clock of the DCS and DAQ must be well synchronised.

- DCS has the equivalence of back end DAQ components as internal building blocks giving access to exchange

of information, understanding of run control commands and sending messages to common message reporting

system.

#### References

- [1] The Semiconductor Tracker Detector Control System Requirements Document, November 15, 1998, EDMS:ATL-IS-ES-0011.

- [2] List of New Requirements to SCT–LV Power supplies, 15 Sep ,1998, <a href="http://www-hep.fzu.cz/Atlas/WorkingGroups/Projects/MSGC/listreq.ps">http://www-hep.fzu.cz/Atlas/WorkingGroups/Projects/MSGC/listreq.ps</a>.

- [3] Comments to US15 cavern, SCT week, June 99, <a href="http://www-hep.fzu.cz/Atlas/WorkingGroups/Projects/MSGC/us15com.ps">http://www-hep.fzu.cz/Atlas/WorkingGroups/Projects/MSGC/us15com.ps</a>.

- [4] ATLAS SCT/pixel Grounding and Shielding note, November 22, 1999, <a href="http://scipp.ucsc.edu/groups/atlas/elect\_doc/SCT\_GND\_SHIELD2.ps">http://scipp.ucsc.edu/groups/atlas/elect\_doc/SCT\_GND\_SHIELD2.ps</a>.

- [5] The Interlock Box for the ATLAS Pixeldetector, Peter Kind, University of Wuppertal, November 5, 1999, <a href="http://www.delphi.uni-wuppertal.de/~kind/INTCDOC1.PS">http://www.delphi.uni-wuppertal.de/~kind/INTCDOC1.PS</a>.

- [6] Drawing of ELMB Motherboard, <a href="http://atlasinfo.cern.ch/ATLAS/GROUPS/DAQTRIG/DCS/LMB/SB/MB/box21.pdf">http://atlasinfo.cern.ch/ATLAS/GROUPS/DAQTRIG/DCS/LMB/SB/MB/box21.pdf</a>.

- [7] DDC User Requirements Document, R. Hart, V.Khomoutnikov, January 26, 2001, <a href="http://atlasinfo.cern.ch/ATLAS/GROUPS/DAQTRIG/DCS/DDC/ddc">http://atlasinfo.cern.ch/ATLAS/GROUPS/DAQTRIG/DCS/DDC/ddc</a> urd.ps

- [8] Irradiation of NTC Resistors, http://www.uni-wuppertal.de/FB8/groups/Drees/detlab/NTC-irradiation.html.

- [9] Evaluation of radiation hard humidity probe, Richard Brenner and Nils Bingefors, To be published as an ATLAS note.